오늘 포스팅에서는 '반도체 설계 전공 대학생을 위한 내 칩(My Chip) 제작 서비스' 관련 소식 전해드리겠습니다.

반도체 설계 전공 대학생을 위한 내 칩(My Chip) 제작 서비스 착수

- '23년 시범 서비스로 약 100명 및 '24년부터 연 500명 이상 칩 제작 목표 -

차별화된 반도체 설계 인재양성을 위한 설계검증 서비스가 본격적으로 시작됩니다.

반도체 설계 전공 학부생·대학원생은 이 서비스를 통해 올해부터 자신이 설계한 칩(Chip)을 제작하여 검증할 수 있는 기회가 생기는데요.

학생들이 설계한 반도체 칩의 제작을 신청하면, 한국전자통신연구원·서울대학교·대구경북과학기술원이 운영하는 반도체 팹(Fab)에서 500nm CMOS(상보형 금속 산화막 반도체) 기술을 이용한 반도체 칩이 제작되고 패키징 되어 설계를 수행한 학생에게 제공될 예정이라고 합니다.

이를 통해 학생들은 자신의 칩(Chip)이 설계한 대로 동작하는지 직접 측정 및 분석을 통해 검증할 수 있게 됩니다.

그동안 반도체 설계를 공부하는 학부생을 위한 칩 제작 기회는 사실상 없었습니다. 석·박사 과정의 대학원생도 주로 상용 파운드리에서 칩 제작을 의뢰하고 있는 상황이었고요. 하지만 이마저도 비싼 금액과 오랜 대기시간, 부족한 피드백 등의 한계가 있어 대다수의 학생들이 칩 제작 기회를 갖기 어려웠습니다.

또한, 전문 파운드리에서 제공하는 피디케이(PDK; Process Design Kits)는 설계자가 알아야 하는 정보로 학생들이 배워야 합니다. 그러나 피디케이(PDK)는 비밀유지계약 하에서 제공되기 때문에, 학부생들에게 제공되기 어렵고 수업에서도 사용되기 어렵습니다.

이러한 이슈들을 해결하기 위해 국내에서 최초로 시도하는 내 칩(My Chip) 제작 서비스는 국내 공공 팹(Fab)을 활용하여 학부생·대학원생에게 무료로 신속하게 칩을 제작해 주고, 관련 사항을 빠르게 피드백할 수 있는 체계로 추진됩니다. 과학기술정보통신부는 본 사업이 실전 역량을 갖춘 설계 인재를 양성하는 매우 실효적인 교육 모델이어서 적극 지원한다는 방침입니다.

학생들을 위한 반도체 설계 검증서비스는 지난달 5월 사업 참여기관이 확정되었으며, 서비스 준비를 거쳐 올해 4/4분기에 시범 서비스를 1회 제공할 예정입니다. 향후 2024년부터 2027년까지 4년 간 매년 6~12회 이상의 설계검증 서비스를 제공하는 것을 목표로 하고 있다고 합니다. 이를 토대로 앞으로 매년 500~1,000명 이상의 설계 전공 학생들이 칩 제작 혜택을 받을 수 있을 것으로 예측됩니다.

- (2023년) 1회 제공 → (2024~2025년) 6회 이상 → (2026~2027년) 12회 이상

참고로 올해 실시하는 설계검증 시범 서비스받기를 희망하는 반도체 설계 분야 학생 및 교수들은 국가나노인프라협의체에 문의하시면 됩니다.

- 문의처: 국가나노인프라협의체 김종석 대리(jongseok.kim@kion.or.kr)

반도체 설계검증 서비스 운영 계획

1차 연도(2023년)

- (기반) 3개 기관 간 표준 공정/소자 기술 확보와 공통 PDK 구축

- (서비스) 첫 해는 PDF가 이미 구축된 한국전자통신연구원에서 설계검증 시범 서비스(TEST MPW) 1회 지원(백업 LOT 추가 진행) 예정

- (추진체계) MPW 지원 대상 선발, 사업운영, 기술사항 등을 자문 심의할 '기술자문위원회'를 산·학·연 중심으로 별도로 구성

2차 연도 이후(2024~2027년)

- (기반) 3개 기관 중 표준 공정/소자 기술 및 공통 PDF 공유 완료

- (서비스) 연 6회 이상의 MPW 제작 지원(백업 LOT 추가진행, '26년 이후에는 연 12회 이상의 MPW 제작 지원)

- (체계) 상시적이고 안정적인 MPW 지원을 위해 참여 대학을 모집하여 관리하며, 정기적인 의견 수렴 및 피드백 제공

- (운영계획) MPW 수요는 국가나노인프라협의체(KION)가 주관하는 나노·반도체 인프라 통합정보시스템과 연계하여 별도 창구 신설 계획('24년)

공공 팹에서 구축한 공통 PDF를 KION에 전달하며, KION은 MPW 접수 시 설계 학생들에게 PDK를 제공

MPW 지원 대상 선발은 수요 접수 후 기술자문위원회에서 기술성·공공성·지원의지 등을 기준으로 별도 심의를 거쳐 선정

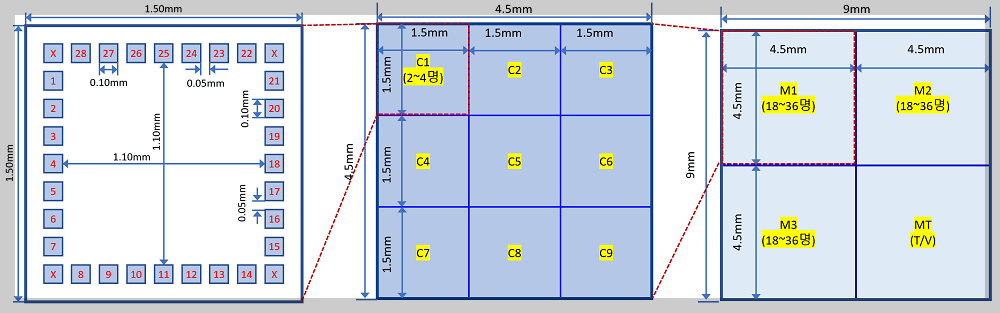

MPW 1회당 25개 팀 이상으로 구성하여 서비스를 제공하고, 1개 팀은 1.5nm × 1.5nm 단위 칩 면적 활용이 가능(연 6회 기준 500~600명 내외 혜택) - 공공 팹에서는 제작된 칩을 별도의 용역을 통해 패키징 공정한 개별 칩을 학생에게 제공

반도체 설계검증 지원 예상 대학(전국 73개교)

| 서울 (17개교) | ||||

| 건국대학교 | 고려대학교 | 광운대학교 | 국민대학교 | 동국대학교(서울) |

| 서강대학교 | 서울대학교 | 서울과학기술대학교 | 서울시립대학교 | 숭실대학교 |

| 연세대학교 | 중앙대학교 | 한성대학교 | 한양대학교 | 홍익대학교 |

| 세종대학교 | 이화여자대학교 | |||

| 경기, 인천 (13개교) | ||||

| 가천대학교 | 경희대학교 | 단국대학교 | 명지대학교 | 성균관대학교 |

| 수원대학교 | 아주대학교 | 평택대학교 | 한국외국어대학교 | 한양대학교(ERICA) |

| 인하대학교 | 인천대학교 | 한국항공대학교 | 선문대학교 | |

| 강원 (4개교) | ||||

| 강릉원주대학교 | 강원대학교 | 연세대학교(미래) | 한림대학교 | |

| 충북 (3개교) | ||||

| 청주대학교 | 충북대학교 | 한국교통대학교 | ||

| 충남, 대전, 세종 (10개교) | ||||

| 공주대학교 | 남서울대학교 | 순천향대학교 | 호서대학교 | KAIST |

| 고려대학교(세종) | 홍익대학교(세종) | 한밭대학교 | 한남대학교 | 충남대학교 |

| 전북 (4개교) | ||||

| 군산대학교 | 원광대학교 | 전북대학교 | 전주대학교 | |

| 전남, 광주 (4개교) | ||||

| 목포해양대학교 | 목포대학교 | 전남대학교 | GIST | |

| 경북, 대구 (9개교) | ||||

| 경북대학교 | 금오공과대학교 | 안동대학교 | 영남대학교 | 포항공과대학교 |

| 한동대학교 | DGIST | 대구가톨릭대학교 | 대구대학교 | |

| 경남, 부산, 울산 (8개교) | ||||

| 경상국립대학교 | 부산대학교 | 창원대학교 | UNIST | 동의대학교 |

| 부경대학교 | 한국해양대학교 | 울산대학교 | ||

| 제주 (1개교) | ||||

| 제주대학교 | ||||

더 자세한 사항은 과학기술정보통신부 누리집을 참고하시기 바랍니다.

감사합니다!

본 정보는 과학기술정보통신부 보도자료를 참고하여 작성하였습니다.

(반도체 설계 전공 대학생을 위한 내 칩(My Chip) 제작 서비스 착수, 2023. 6. 1.)

'전기·전자·통신 > 정책정보' 카테고리의 다른 글

| 통신 4사(KT, SKB, SKT, LGU+) 인터넷 해지 위약금 대폭 인하 (0) | 2023.07.26 |

|---|---|

| 8개 국가첨단전략산업 특화단지 및 9개 국가첨단전략산업 특성화대학 지정 (0) | 2023.07.21 |

| 미래차, 바이오, 반도체 등 5개 소부장특화단지 지정 - 광주, 대구, 충북 오송, 부산, 경기 안성 (0) | 2023.07.21 |

| 온라인 사용전점검 제도 도입으로 접수 신청 당일 즉시 전기공급 가능 (0) | 2023.07.14 |

| 2023년 첨단산업 인재양성 부트캠프 참여대학, 반도체 분야 10개교 선정 (0) | 2023.07.03 |

| 54개 시·군에 소재한 411개 읍·면 농어촌, 5세대 이동통신(5G) 상용화 개시 (0) | 2023.06.23 |

| 반도체 특성화대학 지원사업 수도권 3개교, 비수도권 5개교 선정 (1) | 2023.06.19 |

| 전기안전관리자 선임 규제완화 - 「전기설비 원격감시 및 제어 기능에 관한 고시」제정 (0) | 2023.02.01 |